## EUCLEAK

Side-Channel Attack on the YubiKey 5 Series (Revealing and Breaking Infineon ECDSA Implementation on the Way)

Thomas Roche

NinjaLab, Montpellier, France thomas@ninjalab.io

# **Revision History**

| Revision   | Date | $\mathbf{Author}(\mathbf{s})$ | Description                                                                                                                                                                                                                                                              |

|------------|------|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.0<br>1.1 |      | T. Roche<br>T. Roche          | <ul> <li>Initial Version</li> <li>Add revision history table</li> <li>Minor typo corrections</li> <li>Correct bandpass filter spec.</li> <li>Correct the Infineon SC300 40/65nm family</li> <li>Add/Discuss new certificates</li> <li>Update Project Timeline</li> </ul> |

## ABSTRACT

Secure elements are small microcontrollers whose main purpose is to generate/store secrets and then execute cryptographic operations. They undergo the highest level of security evaluations that exists (Common Criteria) and are often considered inviolable, even in the worst-case attack scenarios. Hence, complex secure systems build their security upon them.

FIDO hardware tokens are strong authentication factors to sign in to applications (any web service supporting FIDO); they often embed a secure element and the FIDO protocol uses *Elliptic Curve Digital Signature Algorithm* (ECDSA for short) as its core cryptographic primitive. YubiKey 5 Series are certainly the most widespread FIDO hardware tokens, their secure element is an Infineon SLE78.

This document shows how - finding a JavaCard open platform (the Feitian A22) based on a similar Infineon SLE78 - we understood the Infineon ECDSA implementation, found a side-channel vulnerability and designed a practical side-channel attack. The attack is then demonstrated on a YubiKey 5Ci. Finally, we show that the vulnerability extends to the more recent Infineon Optiga Trust M and Infineon Optiga TPM security microcontrollers.

Our work unearths a side-channel vulnerability in the cryptographic library of *Infineon Tech*nologies, one of the biggest secure element manufacturers. This vulnerability – that went unnoticed for 14 years and about 80 highest-level Common Criteria certification evaluations – is due to a non constant-time modular inversion.

The attack requires physical access to the secure element (few local electromagnetic side-channel acquisitions, *i.e.* few minutes, are enough) in order to extract the ECDSA secret key. In the case of the FIDO protocol, this allows to create a clone of the FIDO device.

All YubiKey 5 Series (with firmware version below 5.7) are impacted by the attack and in fact all Infineon security microcontrollers (including TPMs) that run the Infineon cryptographic library (as far as we know, any existing version) are vulnerable to the attack. These security microcontrollers are present in a vast variety of secure systems – often relying on ECDSA – like electronic passports and crypto-currency hardware wallets but also smart cars or homes. However, we did not check (yet) that the EUCLEAK attack applies to any of these products.

Cautionary Note: Authentication tokens (like FIDO hardware devices) primary goal is to fight the scourge of phishing attacks. The EUCLEAK attack requires physical access to the device, expensive equipment, custom software and technical skills. Thus, as far as the work presented here goes, it is still safer to use your YubiKey or other impacted products as FIDO hardware authentication token to sign in to applications rather than not using one.

# Contents

| 1 | Intr | roduction 9                                                 |  |  |  |  |  |

|---|------|-------------------------------------------------------------|--|--|--|--|--|

|   | 1.1  | Context                                                     |  |  |  |  |  |

|   | 1.2  | FIDO Hardware Tokens 11                                     |  |  |  |  |  |

|   | 1.3  | Infineon SLE78                                              |  |  |  |  |  |

|   |      | 1.3.1 Feitian A22 JavaCard 14                               |  |  |  |  |  |

|   | 1.4  | Elliptic Curve Digital Signature Algorithm 14               |  |  |  |  |  |

|   |      | 1.4.1         ECDSA Signature Scheme         15             |  |  |  |  |  |

|   |      | 1.4.2 ECDSA Signature Verification Scheme                   |  |  |  |  |  |

|   | 1.5  | Side-Channel Setup and First Observations 16                |  |  |  |  |  |

|   |      | 1.5.1 Side-Channel Setup 16                                 |  |  |  |  |  |

|   |      | 1.5.2 YubiKey 5Ci 17                                        |  |  |  |  |  |

|   |      | 1.5.3 Feitian A22 JavaCard 18                               |  |  |  |  |  |

|   |      | 1.5.4Focus on the Nonce Modular Inversion20                 |  |  |  |  |  |

| 2 | Rev  | erse-Engineering of the Modular Inversion 21                |  |  |  |  |  |

|   | 2.1  | ECDSA Signature Traces                                      |  |  |  |  |  |

|   |      | 2.1.1 Acquisition Campaign                                  |  |  |  |  |  |

|   |      | 2.1.2 Side-Channel Analysis                                 |  |  |  |  |  |

|   |      | 2.1.3 First Hypothesis: Extended Euclidean Algorithm        |  |  |  |  |  |

|   | 2.2  | ECDSA Signature Verification Traces                         |  |  |  |  |  |

|   |      | 2.2.1 Acquisition Campaign                                  |  |  |  |  |  |

|   |      | 2.2.2 Side-Channel Analysis                                 |  |  |  |  |  |

|   |      | 2.2.3 A Timing Leakage                                      |  |  |  |  |  |

|   | 2.3  | Reverse-Engineering of the Modular Inversion Countermeasure |  |  |  |  |  |

|   |      | 2.3.1 Hypothesis                                            |  |  |  |  |  |

|   |      | 2.3.2 Brute-force Experiments                               |  |  |  |  |  |

|   | 2.4  | Conclusions                                                 |  |  |  |  |  |

| 3 | Inni | ut-Recovery Attack on the Extended Euclidean Algorithm 35   |  |  |  |  |  |

| 0 | 3.1  | First Observations                                          |  |  |  |  |  |

|   | 3.2  | Building a Generic Attack Algorithm       37                |  |  |  |  |  |

|   | 3.3  | Simulation Experiments                                      |  |  |  |  |  |

|   | 3.4  | Conclusions                                                 |  |  |  |  |  |

|   |      |                                                             |  |  |  |  |  |

| 4 | Full | Reverse-Engineering of Infineon EEA 43                      |  |  |  |  |  |

|   | 4.1  | More Timing Leakages                                        |  |  |  |  |  |

|   | 4.2  | A Deep Dive into Euclidean Division Algorithms              |  |  |  |  |  |

|   |      | 4.2.1 First Steps                                           |  |  |  |  |  |

|   | 4.3                                                                                      | 4.2.2<br>4.2.3<br>4.2.4<br>Summa                                                            | Failed Attempts                                                                                                                                                                                                                                                                                                                                      | 51<br>52<br>53<br>53                                                  |

|---|------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|

| 5 | <b>Key</b><br>5.1<br>5.2<br>5.3<br>5.4<br>5.5                                            | Input-<br>5.1.1<br>From I<br>Applic<br>5.3.1<br>5.3.2<br>Applic<br>5.4.1<br>5.4.2<br>5.4.3  | very Attack on ECDSA         Recovery Attack on the EEA         Simulation Experiments         Blinded Nonce to ECDSA Long Term Private Key         ation to Feitian A22 JavaCard         Leakage Extraction         Attack Results         ation to YubiKey 5Ci         Side-Channel Acquisitions         Leakage Extraction         Attack Results | <b>55</b><br>56<br>57<br>57<br>57<br>58<br>58<br>58<br>60<br>63<br>63 |

| 6 | <b>Bey</b><br>6.1<br>6.2<br>6.3                                                          | Infineo<br>6.2.1<br>6.2.2                                                                   | LE78         on Security Microcontrollers         on Optiga Trust M         Side-Channel Acquisitions         Leakage Observation         on Optiga TPM         Side-Channel Acquisitions                                                                                                                                                            | 64<br>66<br>66<br>70<br>73<br>73                                      |

| 7 | <ul> <li>7.1</li> <li>7.2</li> <li>7.3</li> <li>7.4</li> <li>7.5</li> <li>7.6</li> </ul> | Confir<br>7.2.1<br>7.2.2<br>7.2.3<br>Potent<br>Attack<br>7.4.1<br>7.4.2<br>Avenue<br>Projec | t on Infineon Security Microcontrollers                                                                                                                                                                                                                                                                                                              | 77<br>78<br>79<br>79<br>79<br>79<br>80<br>80<br>80<br>81<br>81<br>83  |

| A | Yubi                                                                                     | iKey 50                                                                                     | Case Opening                                                                                                                                                                                                                                                                                                                                         | 86                                                                    |

| Β | Infi                                                                                     | neon S                                                                                      | ecurity Microcontrollers                                                                                                                                                                                                                                                                                                                             | 88                                                                    |

# List of Figures

| 1.1  | YubiKey 5 Series Teardowns                                                                                    |

|------|---------------------------------------------------------------------------------------------------------------|

| 1.2  | Feitian A22 JavaCard - Screenshot from SmartCard Focus                                                        |

| 1.3  | YubiKey 5Ci - Teardown                                                                                        |

| 1.4  | YubiKey 5Ci – EM Acquisition Setup                                                                            |

| 1.5  | YubiKey 5Ci – EM Traces – ECDSA Signature                                                                     |

| 1.6  | Feitian A22 JavaCard - EM Acquisition Setup                                                                   |

| 1.7  | Feitian A22 JavaCard - EM Traces - ECDSA Signature                                                            |

| 1.8  | Feitian A22 JavaCard – EM Traces – ECDSA Signature – $(r, s)$ Computation .                                   |

| 2.1  | Feitian A22 JavaCard – ECDSA Signature – Full Trace (Top) - $(r, s)$ Compu-                                   |

|      | tation (Middle) - $k^{-1} \mod N$ Computation (Bottom)                                                        |

| 2.2  | Feitian A22 JavaCard – ECDSA Signature – $k^{-1} \mod N$ Computation (Top) –                                  |

|      | Zoom on Few Iterations (Bottom)                                                                               |

| 2.3  | Feitian A22 JavaCard – ECDSA Signature – $k^{-1} \mod N$ Computation – Inter-                                 |

|      | ruptions Detection (Top) - Cleaned Trace (Bottom)                                                             |

| 2.4  | Feitian A22 JavaCard – ECDSA Signature – $k^{-1} \mod N$ Computation – Itera-                                 |

|      | tions Detection (Top) - Zoom on Few Iterations (Bottom)                                                       |

| 2.5  | Feitian A22 JavaCard – ECDSA Signature – $k^{-1} \mod N$ Computation – Dis-                                   |

|      | tribution of the Number of Iterations – Observations (Blue) - EEA Simulations                                 |

|      | (Orange)                                                                                                      |

| 2.6  | Feitian A22 JavaCard - ECDSA Signature Verification - Full Trace                                              |

| 2.7  | Feitian A22 JavaCard - ECDSA Signature Verification - Full Trace (Top) -                                      |

|      | Zoom Between the Scalar Multiplications (Middle) - $s^{-1} \mod N$ Computation                                |

|      | (Bottom)                                                                                                      |

| 2.8  | Feitian A22 JavaCard – ECDSA Signature Verification – $s^{-1} \mod N$ Computa-                                |

|      | tion – Interruptions Detection (Top) - Cleaned Trace (Bottom)                                                 |

| 2.9  | Feitian A22 JavaCard – ECDSA Signature Verification – $s^{-1} \mod N$ Computa-                                |

|      | tion – Iterations Detection (Top) - Zoom on Few Iterations (Bottom)                                           |

| 2.10 | Feitian A22 JavaCard - ECDSA Signature Verification - $s^{-1} \mod N$ - Four                                  |

|      | Consecutive Iterations                                                                                        |

| 2.11 | Feitian A22 JavaCard - ECDSA Signature Verification - 100 Superposed Odd                                      |

|      | Iterations – $\Delta_{r_0,r_1} = 0$ (Top) - $\Delta_{r_0,r_1} = 1$ (Middle) - $\Delta_{r_0,r_1} = 2$ (Bottom) |

| 2.12 | Feitian A22 JavaCard - Modular Inversion Multiplicative Mask Brute Force -                                    |

|      | Pearson Correlation Results $\rho(\{\Delta_{r_0,r_1}\}_{0 \le i \le n}, \{\mathcal{L}_i\}_{0 \le i \le n})$   |

| 3.1  | A Generic Input-Recovery Side-Channel Attack on the <b>EEA</b>                                                |

| 3.2  | Simulation of the Generic Attack – $\mathcal{L}_i = q_i$                                                      |

| 4.1                                       | Feitian A22 JavaCard - ECDSA Signature Verification - $\Delta_{r_0,r_1} = 2 - 100$ Su-                                                                                                |                                         |

|-------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|

|                                           | perposed Odd Iterations (Top) - A Single Trace, Zoom on the New Leakage Area (Bottom)                                                                                                 | 44                                      |

| 4.2                                       | Feitian A22 JavaCard – ECDSA Signature Verification – Odd Iteration with $\Delta_{r_0,r_1} = 2$ – Various Shapes in the EM Signal                                                     | 45                                      |

| 4.3                                       | Feitian A22 JavaCard – ECDSA Signature Verification – EEA Computation –<br>Full Trace (Top) - Zoom around the First Iterations (Bottom)                                               | 46                                      |

| 4.4                                       | Feitian A22 JavaCard – ECDSA Signature Verification – EEA Computation<br>Pattern Detection – Two Consecutive Iterations (Top) - Several Iterations (Mid-                              |                                         |

|                                           | dle) - Full Trace (Bottom)                                                                                                                                                            | 47                                      |

| 4.5                                       | Feitian A22 JavaCard - ECDSA Signature Verification - EEA Computation - Resynchronized Iteration - Full Iteration (Top) - Zoom (Bottom)                                               | 48                                      |

| 4.6                                       | Feitian A22 JavaCard – ECDSA Signature Verification – EEA Computation –<br>Resynchronized Iteration – Compact Iteration (Top) - Regular Iteration (Bottom)                            | 49                                      |

| 4.7                                       | Feitian A22 JavaCard – ECDSA Signature Verification – EEA Computation –<br>Full Trace with <i>Compact</i> Areas                                                                       | 49                                      |

| 4.8                                       | Feitian A22 JavaCard – ECDSA Signature Verification – EEA Computation –<br>Resynchronized Iteration – $\Delta_{r_0,r_1} = 2$ , quotient = 2 – Case 1 (Top) - Case 2                   | 10                                      |

| 1.0                                       | (Middle) - Case 3 (Bottom)                                                                                                                                                            | 50                                      |

| 4.9                                       | Feitian A22 JavaCard – ECDSA Signature Verification – EEA Computation –<br>Resynchronized Iteration – $\Delta_{r_0,r_1} = 3$ , quotient = 6 (Top) - $\Delta_{r_0,r_1} = 3$ , quotient |                                         |

|                                           | $= 4 \text{ (Bottom)} \dots \dots$                                              | 51                                      |

| 5.1                                       | Simulation of the Generic Attack – Comparison Between $\mathcal{L}_i = q_i$ and Infineon Leakage                                                                                      | 56                                      |

| $5.2 \\ 5.3$                              | YubiKey 5Ci – ECDSA Signature – $k^{-1} \mod N$ Computation                                                                                                                           | 59                                      |

| 5.4                                       | Zoom on Several Iterations (Middle) - Zoom on Two Consecutive Iterations (Bottom)<br>YubiKey $5Ci - ECDSA$ Signature $-k^{-1} \mod N$ Computation – Iterations Detec-                 | 60                                      |

| 5.5                                       | tion (Top) - Zoom on Few Iterations (Bottom)                                                                                                                                          | 61                                      |

|                                           | Subtrace                                                                                                                                                                              | 61                                      |

| 5.6                                       | YubiKey 5Ci – ECDSA Signature – $k^{-1} \mod N$ Computation – Single Iteration – 2 Different Odd Iterations (First and Third) - After Averaging Rolling Window                        |                                         |

|                                           | (Second and Last)                                                                                                                                                                     | 62                                      |

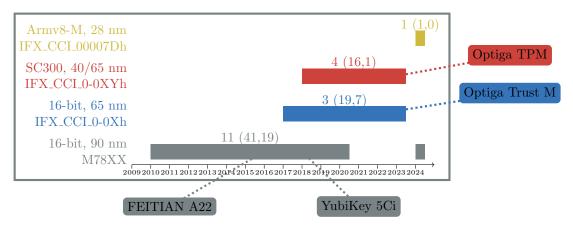

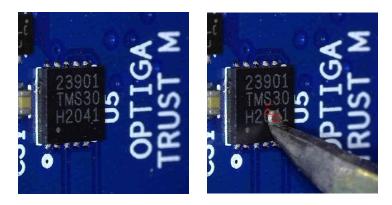

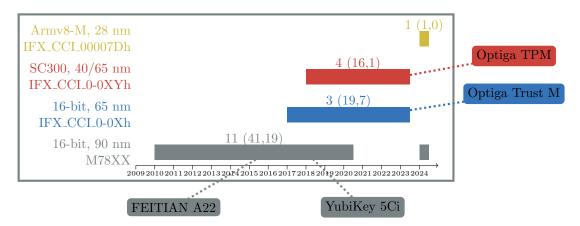

| $\begin{array}{c} 6.1 \\ 6.2 \end{array}$ | Infineon Security Microcontroller Families                                                                                                                                            | $\begin{array}{c} 65 \\ 66 \end{array}$ |

| $\begin{array}{c} 6.3 \\ 6.4 \end{array}$ | Optiga Trust M - Acquisition Setup                                                                                                                                                    | $\begin{array}{c} 67 \\ 67 \end{array}$ |

| 6.5                                       | <b>Optiga Trust</b> M – ECDSA Signature – Full Trace (Top) - Zoom in Computation<br>End (Middle) - $k^{-1}$ mod N Computation (Bottom)                                                |                                         |

| 6.6                                       | Optiga Trust M – ECDSA Signature Verification – Full Trace (Top) - Zoom be-                                                                                                           | 69                                      |

| 6.7                                       | fore Double Scalar Mult. (Middle) - $s^{-1} \mod N$ Computation (Bottom) Optiga Trust M – ECDSA Signature Verification – Full Trace                                                   | $70 \\ 71$                              |

| 6.8                                       | Optiga Trust M – ECDSA Signature Verification – Cleaned $s^{-1} \mod N$ Computation (Top) - Single Odd Iteration after Splitting (Bottom)                                             | 72                                      |

| 6.9<br>6.10                               | Optiga Trust M – ECDSA Signature Verification – 100 superposed Odd Iterations)<br>Optiga TPM – OPTIGA TPM 9673 RPI EVAL                                                               | $72 \\ 73$                              |

|                                           |                                                                                                                                                                                       |                                         |

| 6.11 | Optiga TPM - Acquisition Setup                                            | 74  |

|------|---------------------------------------------------------------------------|-----|

| 6.12 | Optiga TPM-ECDSA Signature Verification-Full Trace (Top) - Zoom on ECDSA  |     |

|      | Operation (Bottom)                                                        | 75  |

|      | Optiga TPM – ECDSA Signature Verification – Full Computation (Top) - Zoom |     |

|      | on $s^{-1} \mod N$ Computation (Middle) - Zoom on Few Iterations (Bottom) | 76  |

| 4 1  |                                                                           | 0.0 |

|      | Brand New YubiKey 5C                                                      |     |

|      | YubiKey 5C - First Opening                                                |     |

| A.3  | YubiKey 5C - Second Opening                                               | 87  |

# List of Tables

| $2.1 \\ 2.2$ | Acquisition parameters on Feitian A22 JavaCard – ECDSA Signature<br>Acquisition parameters on Feitian A22 JavaCard – ECDSA Signature Verification                                                                                                                                     |                      |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| $5.1 \\ 5.2$ | Number of Different Sets of Iterations $w.r.t. \Delta_{r_0,r_1} \dots \dots \dots \dots \dots \dots$<br>Acquisition parameters on YubiKey 5Ci – ECDSA Signature                                                                                                                       | $58 \\ 59$           |

|              | Acquisition parameters on Optiga Trust M – ECDSA Signature Acquisition parameters on Optiga Trust M – ECDSA Signature Verification Acquisition parameters on Optiga TPM – ECDSA Signature Verification                                                                                | 68<br>71<br>75       |

| B.2<br>B.3   | Infineon Security Microcontrollers – M78XX (SLE78) – 16-bit, 90 nm Infineon Security Microcontrollers – IFX_CCI_0-0Xh – 16-bit, 65 nm Infineon Security Microcontrollers – IFX_CCI_0-0XYh – ARM SC300, 40/65 nm Infineon Security Microcontrollers – IFX_CCI_00007Dh – Armv8-M, 28 nm | 88<br>89<br>89<br>89 |

# List of Algorithms

| 1 | Extended Euclidean Algorithm for Modular Inversion                                                    | 26 |

|---|-------------------------------------------------------------------------------------------------------|----|

|   | Extended Euclidean Algorithm for Modular Inversion (repeated from page 26) A Generic Attack Algorithm |    |

|   | Truncated Extended Euclidean Algorithm                                                                |    |

| 4 | Euclidean Division Algorithm                                                                          | 53 |

# Chapter 1 Introduction

### 1.1 Context

Secure elements are the root of trust of secure systems. These little pieces of hardware should be able to generate, store and manipulate secrets while ensuring their full confidentiality and integrity. And, more importantly, they must be able to do so even when falling inside the adversary hands. To fulfill this requirement, the secure elements follow the *simpler-is-safer* rule: keep the hardware simple, keep the software simple, keep the communication protocols simple. By keeping the functionalities to a bare minimum (generate and store cryptographic keys and certificates, sign documents, verify signatures and wrap secret keys), secure elements manufacturers must fight the endless urge of making things more powerful, more complex, more everything.

By keeping things simple, the attack surface is small and easier to audit. The most stringent certification scheme of security devices is under the umbrella of *Common Criteria* (CC for short) and was preliminary designed for smart cards evaluation <sup>1</sup>. This evaluation, organized around certification bodies (public institutions from the signatory countries of the SOGIS <sup>2</sup>), is executed by an independent and accredited ITSEF laboratory. These evaluations are tedious and extremely time consuming, especially when aiming at the highest security level: AVA\_VAN\_5 <sup>3</sup>. Hence, secure elements manufacturers must face the marketing challenge of selling what might seem outdated hardware technology <sup>4</sup> along with epsilonesque functionality updates but for a important time-to-market production due to certification delays.

Integrated in a public key infrastructure, secure elements allow to safely – with unparalleled security guarantees – authenticate a genuine product (*e.g.* for access control) or validate that a piece of software was not modified (*e.g.* for boot purpose). Secure elements are then everywhere, from the Trusted Platform Modules (TPM for short) that can be found managing the secure boot of most computers (personal or server), to the banking or ID cards that can be found in everybody's pocket. They are also omnipresent in high-end smartphones (notably for payment purpose), in cars and more generally in any IoT device that requires (or advertises) high level of security.

<sup>&</sup>lt;sup>1</sup>https://www.commoncriteriaportal.org/files/ppfiles/ssvgpp01.pdf

<sup>&</sup>lt;sup>2</sup>https://www.sogis.eu/

$<sup>^{3} \</sup>rm The$  Vulnerability Assessment Number, it goes from 1 to 5. The CC EAL level aggregates, among other things, the AVA\_VAN\_X level

<sup>&</sup>lt;sup>4</sup>Most common technology node for smart cards is 40nm nowadays.

In the last decade secure elements made their way inside two new kind of products: cryptocurrency hardware wallets and FIDO hardware tokens. Both of these products claim high level of security while being easily in the hand of an adversary: the perfect use case for secure elements. As secure elements penetration testers, NinjaLab is obviously interested in these products and more particularly into FIDO hardware tokens. Indeed, while undergoing the most thorough security evaluations from highly skilled ITSEF laboratories, some vulnerabilities have been found in the past by independent security researchers. The ROCA attack [22] and the TPM-Fail attack [21] are certainly the most important ones in the recent years.

In 2021 NinjaLab published A Side Journey to Titan [19, 27], reporting a side-channel vulnerability in the P5x family of security microcontrollers. The P5x are old secure elements from NXP <sup>5</sup> manufacturer that still could be found in some products (they are slowly replaced by the P6 and P7 families from the same manufacturer), and notably in the Google FIDO hardware token: the Google Titan Security Key <sup>6</sup>. Note that the Google Titan Security Key was recently updated to support passkey <sup>7</sup>: passwordless FIDO authentication. In [19], NinjaLab reported a side-channel vulnerability in the Elliptic Curve Digital Signature Algorithm (ECDSA for short) implementation of NXP that could be exploited with a physical access to the device <sup>8</sup> for about 10 hours (and an offline phase of about 6 hours, that can be done when the device is already given back to the legitimate user).

In the present work, NinjaLab unveils a new side-channel vulnerability in the ECDSA implementation of Infineon <sup>9</sup> on any security microcontroller family of the manufacturer. This vulnerability lies in the ECDSA ephemeral key (or nonce) modular inversion, and, more precisely, in the Infineon implementation of the *Extended Euclidean Algorithm* (EEA for short). To our knowledge, this is the first time an implementation of the EEA is shown to be vulnerable to side-channel analysis (contrarily to the EEA binary version, *e.g.* [9, 2, 1]). The exploitation of this vulnerability is demonstrated through realistic experiments and we show that an adversary only needs to have access to the device for few minutes. The offline phase took us about 24 hours; with more engineering work in the attack development, it would take less than one hour.

After a long phase of understanding Infineon implementation through side-channel analysis on a Feitian <sup>10</sup> open JavaCard smartcard, the attack is tested on a YubiKey 5Ci, a FIDO hardware token from Yubico. All YubiKey 5 Series (before the firmware update 5.7 <sup>11</sup> of May 6th, 2024) are affected by the attack. In fact all products relying on the ECDSA of Infineon cryptographic library running on an Infineon security microcontroller are affected by the attack. We estimate that the vulnerability exists for more than 14 years in Infineon top secure chips. These chips and the vulnerable part of the cryptographic library went through about 80 CC certification evaluations of level AVA\_VAN\_4 (for TPMs) or AVA\_VAN\_5 (for the others) from 2010 to 2024 (and a bit less than 30 certificate maintenances).

A coordinated responsible disclosure has been conducted with Infineon (we naturally included

<sup>8</sup>or more generally any device running the ECDSA on a P5x secure element

<sup>9</sup>https://www.infineon.com/

<sup>&</sup>lt;sup>5</sup>https://www.nxp.com/

<sup>&</sup>lt;sup>6</sup>https://store.google.com/fr/product/titan\_security\_key?hl=fr

<sup>&</sup>lt;sup>7</sup>See https://blog.google/technology/safety-security/titan-security-key-google-store/

<sup>&</sup>lt;sup>10</sup>https://www.ftsafe.com/Products/Card\_OS

<sup>&</sup>lt;sup>11</sup>https://www.yubico.com/blog/empowering-enterprise-security-at-scale-with-new-productinnovations-yubikey-5-7-and-yubico-authenticator-7/

Yubico and Feitian, as well as the certification bodies BSI  $^{12}$  and ANSSI  $^{13}$  in the responsible disclosure). The responsible disclosure started on April the 19th 2024 and Infineon confirmed (July  $26^{th}$ , 2024) that they have implemented and tested a patch to their library, eliminating the attack threat.

Necessary information about FIDO protocol, ECDSA and our side-channel acquisition chain are presented in the remainder of this introduction while the following chapters present, in all technical details:

- a first side-channel reverse-engineering of the ECDSA implementation, and more particularly of the nonce modular inversion, leading to the identification of a sensitive leakage (Chapter 2);

- the design of a generic and flexible side-channel attack on the Extended Euclidean Algorithm (Chapter 3);

- a deeper reverse-engineering of Infineon implementation to uncover stronger sensitive leakages (Chapter 4);

- the successful application of the attack on Feitian A22 JavaCard and YubiKey 5Ci products (Chapter 5);

- the demonstration that this vulnerability is not limited to SLE78 but also to all the subsequent families of Infineon security microcontrollers (Chapter 6).

Finally, Chapter 7 presents the attack impact analysis (by no means comprehensive), a simple mitigation solution that Infineon chose to follow, several directions of research opened by this work and finally the whole project timeline.

### **1.2 FIDO Hardware Tokens**

FIDO Hardware tokens are USB and/or NFC devices (sometimes Bluetooth) that allow a user to setup a factor of authentication while sign in to a web service account that supports FIDO protocol <sup>14</sup> (e.g. a Google account). This authentication factor can be added to a traditional login/password authentication (in that case our attack requires that the attacker also knows the login/password of the target, e.g. using phishing) or as a unique factor of authentication (as specified in the FIDO2 protocol and often refereed to as the FIDO2 Passwordless Authentication or Passkey functionality).

For the purpose of this document, we do not need to go into the details of the FIDO protocol – interested readers can have a look to [19] where we took some time to explain the basic principles. Here, what we need to know can be summarized as follows <sup>15</sup>:

• when registering a new FIDO token in the user account, an ECDSA key pair is generated inside the device. The device sends to the remote server the public key and stores the private key;

<sup>12</sup> https://www.bsi.bund.de/DE/Home/home\_node.html

<sup>&</sup>lt;sup>13</sup>https://cyber.gouv.fr/

<sup>&</sup>lt;sup>14</sup>See https://www.yubico.com/works-with-yubikey/catalog/ for a list of almost all applications supporting FIDO protocol

<sup>&</sup>lt;sup>15</sup>The ECDSA scheme is formally described in Section 1.4

• when signing in, the remote sever sends a challenge that is signed by the FIDO token using the associated private key. The remote server can confirm the presence of the token by verifying the signature (using the public key shared during the registration phase).

**Side-channel attack scenario** Here is a natural side-channel attack scenario (as proposed initially in [19]):

- 1. the adversary steals the login and password of a victim's application account protected with FIDO (e.g. via a phishing attack);

- 2. the adversary gets physical access to the victim's device during a limited time frame, without the victim noticing;

- 3. thanks to the stolen victim's login and password (for a given application account), the adversary sends the authentication request to the device as many time as necessary<sup>16</sup> while performing side-channel measurements;

- 4. the adversary quietly gives back the FIDO device to the victim;

- 5. the adversary performs a side-channel attack over the measurements, and succeeds in extracting the ECDSA private key linked to the victim's application account;

- 6. the adversary can sign in to the victim's application account without the FIDO device, and without the victim noticing. In other words the adversary created a clone of the FIDO device for the victim's application account. This clone will give access to the application account as long as the legitimate user does not revoke its authentication credentials.

While the first version of the Google Titan security key embeds a P5x secure element from NXP, Yubico – the leader of FIDO hardware tokens – relies on the more recent SLE78 secure element from Infineon. One of the advantages of the SLE78 chip is that there exists a USB version, allowing to build a USB secure token with a single chip (the SLE78 handling both the secure element functionalities and the USB communication). This is the "industry's first FIDO2 certified Reference Design based on the SLE78 single-chip solution" <sup>17</sup> and seems pretty attractive for designing FIDO hardware token. Also, compared to NXP P5x secure elements, the SLE78 family is more recent and has still active AVA\_VAN\_5 (and in fact EAL 6+) CC certificates.

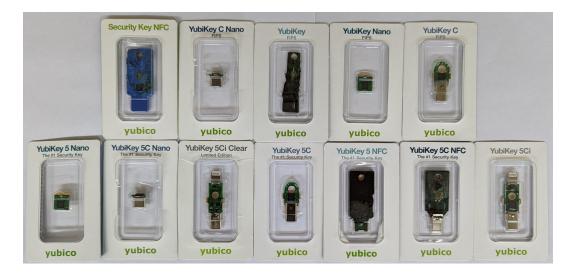

For the interested readers of an overview of the internals of many FIDO hardware tokens, we strongly encourage to have a look to Victor Lomné presentation at Hardwear.io NL 2022 conference [18]. Figure 1.1 is directly taken from this presentation and shows the teardown of all YubiKey 5 Series. All of them embed an Infineon SLE78CLUFX5000 secure microcontroller, this will be our new target of investigation. However, the FIDO protocol does not allow to choose (or even know) any private key generated inside the device. To ease the understanding of Infineon implementation and the research of a vulnerability, we first need to find a product where one can know the private key, also called a *training device* (this was also the direction chosen in [19], with success). We then first look for a *JavaCard open platform* that embed a SLE78, indeed JavaCard open platforms offer a richer user cryptographic API through the development of JavaCard applets.

$<sup>^{16}</sup>$ This can be done while actually signing in to the remote server or not. In the former case, this would make the FIDO counter countermeasure useless but necessitate to have either a small number of ECDSA executions to perform or a lot of time.

<sup>&</sup>lt;sup>17</sup>https://fidoalliance.org/tech-industry-leaders-ship-fido2-certified-solutions-to-reduce-password-use-on-the-web/

Figure 1.1: YubiKey 5 Series Teardowns

### **1.3 Infineon SLE78**

When considering only AVA\_VAN\_5 secure elements (*i.e.* the most secure chips that exist), the Infineon SLE78 family is one of the most common in the field. It has been designed for banking and ID applications and successfully took an important market share. The microcontroller is a proprietary design from Infineon, from the many public CC certification reports of chips from the SL78 family <sup>18</sup>, we have:

"The [SLE78] provides a real 16-bit CPU-architecture and is compatible to the Intel 80251 architecture. The major components of the core system are the dual CPU (Central Processing Units), the MMU (Memory Management Unit) and MED (Memory Encryption/Decryption Unit). The dual interface controller is able to communicate using either the contact based or the contactless interface."

Infineon SLE78, like any secure element, embeds several dedicated hardware cryptographic co-processors, notably a modular arithmetic co-processor which can be used, though a cryptographic library (we will sometimes use *cryptolib*, for short), to securely (and efficiently) execute public-key cryptography like RSA or ECC. Infineon provides an optional cryptolib implementing such cryptographic operations.

The YubiKey 5 Series are based on a SLE78 IC version M7893~B11 with Infineon EC cryptolib version 1.03.006<sup>19</sup>, information that can be found in the ANSSI CSPN (Certificat de Sécurité de Premier Niveau) security target document<sup>20</sup>.

<sup>&</sup>lt;sup>18</sup>See e.g. https://www.bsi.bund.de/SharedDocs/Downloads/DE/BSI/Zertifizierung/Reporte/Reporte07/ 0782V5a\_pdf

<sup>&</sup>lt;sup>19</sup>M7893 B11 with EC library v1.03.006: last CC certification (EAL6+) in 2018, https://www.bsi.bund.de/ SharedDocs/Downloads/DE/BSI/Zertifizierung/Reporte/Reporte08/0879V3a\_pdf

<sup>&</sup>lt;sup>20</sup>https://cyber.gouv.fr/sites/default/files/2021/09/anssi-cible-cspn-2021\_18en.pdf, page 18, Table 5

### 1.3.1 Feitian A22 JavaCard

When looking for JavaCard open platforms that embed a SLE78, the Feitian A22 JavaCard product was cheap and easy to purchase (see Figure 1.2 from SmartCard Focus reseller site <sup>21</sup>).

| Smartcard <sup>(1)+44 (0)1428 685</sup><br>Fécus номе <b>внор</b>                                         | 250 🗸 stock 🗸 service 🗸 sup          | port                      |                                                                                                                                       |                                                                                                                                    |

|-----------------------------------------------------------------------------------------------------------|--------------------------------------|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

| Fõcus home shope                                                                                          | BLOG RESOURCES ABO                   | JT US CONTACT US          |                                                                                                                                       |                                                                                                                                    |

| Products  CARDS  FIDD KEYS AND CARDS  FIDD KEYS AND CARDS  STARTERDEVELOPMENT KITS  READERS               | JavaCOS A22 dual ir                  | iterface Java card - 1501 | K<br>Availability: In stock ()<br>BUY<br>QY 1                                                                                         | EUR 7.54                                                                                                                           |

| SOFTWARE     ACCESSORIES     Applications     LogGNAUTHENTICATION     NHSHEALTHCARE     DIGTAT TACHORAPHS |                                      |                           | Units<br>1+<br>10+<br>100+<br>250+<br>Prices shown are per unit, excluding VAT and<br>Piesas contact us for volume and reseller prici |                                                                                                                                    |

| NFC     REIDINFC APP INTEGRATION     DOOR ACCESS CONTROL     MOBILE PHONE SIM                             | functionality, supporting T=0 or T=3 |                           |                                                                                                                                       | ser RAM. This card is designed for both contact and contactless<br>only. Let us know if this is important for your application, as |

| Manufacturers           ACS           BASICCARD           CERTGATE           DOT ORIGIN           EASTTAC |                                      |                           | Global Platform 2.1.1 specifications, running on the Ir<br>Royment environments, the card is also supported by                        | dinwon SLE78 <mark>pl</mark> atform.<br>a FREE Java card applet development environment, available on                              |

| ELATEC                                                                                                    |                                      |                           |                                                                                                                                       |                                                                                                                                    |

Figure 1.2: Feitian A22 JavaCard - Screenshot from SmartCard Focus

On a JavaCard open platform, we can develop and push our own JavaCard applet and run all cryptographic primitives supported by the JavaCard API and implemented by the JavaCard OS of the card. This JavaCard (or a similar one from Feitian) has been certified EAL5+ under Common Criteria  $^{22}$ . This certification is from 2018 and involves SLE78 IC version *M7892 B11* with Infineon EC cryptolib version 1.02.013  $^{23}$ .

This is not exactly the same SLE78 hardware version nor cryptolib version than the YubiKey 5 Series, we will assume it is close enough.

On Feitian A22 JavaCard, the JavaCard OS happens to follow JavaCard 2.2.2 specifications [24], we hence developed and loaded a custom JavaCard applet <sup>24</sup> allowing us to freely control the JavaCard ECDSA signature engine on Feitian A22 JavaCard. More precisely, we can load chosen long term ECDSA private keys, perform ECDSA signatures and ECDSA signature verifications.

### 1.4 Elliptic Curve Digital Signature Algorithm

In this section we recall some basic information about ECDSA as well as introduce the notations we will use in this document. It is worth noting here that the FIDO protocol is specified on the 256-bit elliptic curve P256 [23], and then, w.l.o.g., all our tests are done on this curve. Hence, for our simulations, the elliptic curve order N is that of P256 curve and the nonce k is always a random of binary size up to 256 bits.

<sup>&</sup>lt;sup>21</sup>https://www.smartcardfocus.com/shop/ilp/id~712/javacos-a22-dual-interface-java-card-150k/p/

<sup>22</sup>https://www.commoncriteriaportal.org/files/epfiles/SERTIT-091CRFeitianv1.0.pdf

<sup>&</sup>lt;sup>23</sup>M7892 B11 with EC library v1.02.013: last CC certification (EAL6+) in 2020, https://www.bsi.bund.de/ SharedDocs/Downloads/DE/BSI/Zertifizierung/Reporte/Reporte07/0782V5a\_pdf

<sup>&</sup>lt;sup>24</sup>Thanks notably to the great open-source project for building JavaCard applets [20]

### 1.4.1 ECDSA Signature Scheme

The ECDSA signature scheme is the main target of our attack. Here is a rough sketch of the scheme (taken from [19] with slightly different notations):

- elliptic curve E over prime field  $\mathbb{F}_p$ , elliptic curve base point is  $G_{(x,y)}$  of order N

- inputs: long term private key d, hash digest of the input message to sign h = H(m)

- 1. randomly generate a nonce k in  $\mathbb{Z}/N\mathbb{Z}$

- 2. scalar multiplication  $Q_{(x,y)} = [k]G_{(x,y)}$

- 3. denote by r the x-coordinate of Q:  $r = Q_x$

- 4. compute  $s = k^{-1}(h + rd) \mod N$

- output: (r,s)

**First Remark:** We can find the nonce k from the signature (r, s) of digest h with the knowledge of the private key d:

$$k = s^{-1}(h + rd) \mod N \tag{1.1}$$

Inversely, knowing the nonce k is enough to find the private key d:

$$d = r^{-1}(ks - h) \bmod N$$

**Second Remark:** An usual countermeasure against side-channel analysis is to randomize the base point at each scalar multiplication (see [3]). So instead of computing directly the scalar multiplication  $[k]G_{(x,y)}$  on the affine coordinates of G, one might uses the projective coordinates of G:

- 1. randomly generate a random z in  $\mathbb{F}_p$

- 2. send  $G_{(x,y)}$  to its projective coordinates (xz, yz, z)

- 3. compute  $Q_{(x,y,z)} = [k]G_{(x,y,z)}$

- 4. get the x affine coordinate of  $Q_{(x,y,z)}$ :  $r = x/z \mod p$

### 1.4.2 ECDSA Signature Verification Scheme

As mentioned before, one great advantage of working on the Feitian A22 JavaCard is the possibility to run the ECDSA signature verification algorithm (and not only the signature algorithm as on YubiKey 5 Series). As we will see, the signature verification algorithm requires to compute similar operations than in the signature algorithm, this might provide additional information on their implementation. Moreover, developers might downgrade countermeasures to improve the execution time. Indeed, the signature verification algorithm does not involve any secret and then side-channel or fault injection countermeasures seem useless speed reducers. For reverse engineering however, such a countermeasure downgrade is a windfall, it provides the opportunity to learn a lot on the implementation and its countermeasures.

Here is a rough sketch of the ECDSA signature verification scheme (taken from [19] with slightly different notations):

- elliptic curve E over prime field  $\mathbb{F}_p$ , elliptic curve base point is  $G_{(x,y)}$  and order is N

- inputs: public key  $P_{(x,y)}$ , the hash of the signed input message h = H(m)

- inputs: the signature to be verified (r, s)

- 1. compute first scalar  $k^{(1)} = s^{-1}r \mod N$

- 2. compute second scalar  $k^{(2)} = s^{-1}h \mod N$

- 3. first scalar multiplication  $Q_{(x,y)}^{(1)} = [k^{(1)}]P_{(x,y)}$

- 4. second scalar multiplication  $Q_{(x,y)}^{(2)} = [k^{(2)}]G_{(x,y)}$

- 5. compute  $\bar{r} = Q_x^{(1)} + Q_x^{(2)} \mod N$

- 6. check that  $\bar{r} = r$

**First Remark:** One can compute  $k^{(1)}$  and  $k^{(2)}$  from the public inputs.

**Second Remark:** The two scalar multiplications can be executed in a single pass using a *double* scalar multiplication approach. One way to do so is to pre-compute  $Q_{(x,y)} = P_{(x,y)} + G_{(x,y)}$  and then follow a simple double-and-add algorithm where, at each iteration, one bit of  $k^{(1)}$  and one bit of  $k^{(2)}$  are processed.

### **1.5** Side-Channel Setup and First Observations

Let us briefly present the side-channel setup we used for our analysis.

### 1.5.1 Side-Channel Setup

In order to perform electromagnetic (EM for short) side-channel measurements over the two targets, we used the following hardware parts:

- Langer ICR HH 500-6 near-field EM probe with an horizontal coil of diameter  $500\mu$ m and a frequency bandwidth from 2MHz to 6GHz with its Langer BT 706 bias-tee [15];

- Thorlabs PT3/M three axes (X-Y-Z) manual micro-manipulator with a precision of 10µm [28];

- Dino-Lite digital microscope AM4113TL [4];

- Pico Technology PicoScope 6424E oscilloscope [25], with a 500MHz frequency bandwidth, sampling rate up to 5GSa/s, 4 channels, a shared channel memory of 4G samples max. and 8-bit to 12-bit ADC resolution;

- LeCroy WavePro 254HD oscilloscope, with a 2.5GHz frequency bandwidth, sampling rate up to 20GSa/s, 4 channels and a memory of 5G samples max. per channel with 12-bit ADC resolution [16];

- Ledger Scaffold electronic board [17].

Note that the cost of this setup is about  $10k \in$  (including the cost of the computer used for processing side-channel measurements). The LeCroy WavePro oscilloscope with 12-bit resolution raises the cost (it has been used for the Yubikey acquisitions) by about  $30k \in$ , but we are confident that the PicoScope set with 8-bit ADC resolution would have been completely sufficient for the attack.

#### 1.5.2 YubiKey 5Ci

Accessing the SLE78 on a YubiKey requires to open the plastic case and access the logic board. From Victor Lomné teardowns of the whole family of YubiKey 5 Series (see Figure 1.1 and [18]), the YubiKey 5Ci seemed in good shape, so we selected it (see Figure 1.3). At the end of this project, we wanted to estimate the difficulty for an attacker to remove the plastic case of a YubiKey. However, by that time (two years have passed), Victor did not remember how hard it was. From Figure 1.1 one can tell that the NFC and FIPS version of the YubiKey were quite difficult to open and the result leads (in the case of Victor's not so careful opening) to destroy the product. However, for the rest, it is difficult to tell. So we bought two new YubiKey 5C from Yubico. The package opening of these two devices is presented in Annex A. This study was done after the YubiKey 5.7 firmware update of the 6th May 2024 that moves the firmware to a new cryptography library <sup>25</sup>.

We hence could validate, by the observation of the side-channel execution traces of these new devices, that the new implementation is not vulnerable to the attack presented in this report.

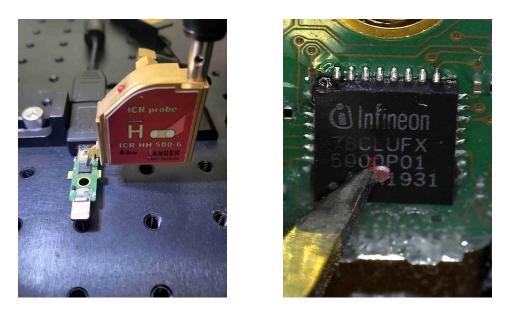

Figure 1.3: YubiKey 5Ci - Teardown

The EM acquisition setup is depicted on Figure 1.4, with the correct position of the EM probe to acquire the signal.

<sup>&</sup>lt;sup>25</sup>https://www.yubico.com/blog/empowering-enterprise-security-at-scale-with-new-product-innovations-yubikey-5-7-and-yubico-authenticator-7/

Figure 1.4: YubiKey 5Ci - EM Acquisition Setup

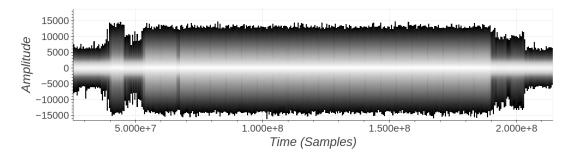

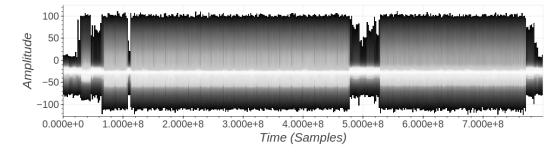

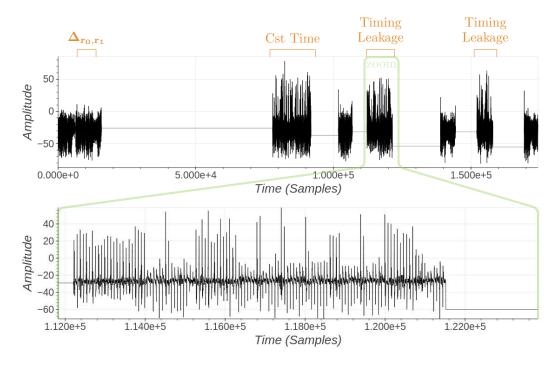

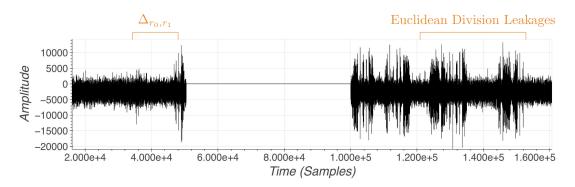

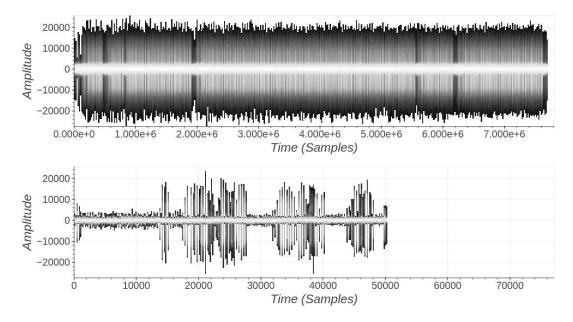

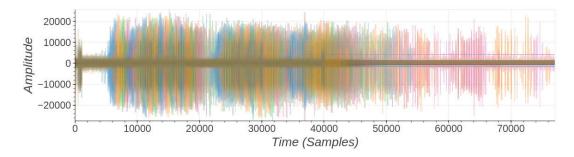

Figure 1.5 shows a side-channel execution trace of an ECDSA signature acquired with the above setup. The acquisition is triggered directly from the EM signal, on a pattern present at the beginning of the EM activity of the command processing the authentication request message of the FIDO protocol.

Figure 1.5: YubiKey 5Ci - EM Traces - ECDSA Signature

### 1.5.3 Feitian A22 JavaCard

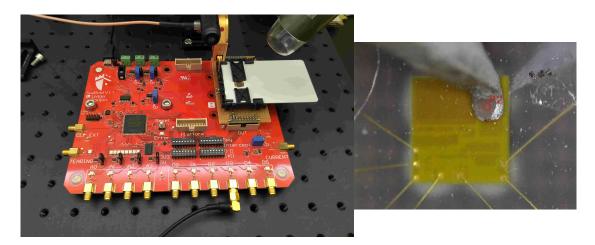

To communicate and acquire both power and EM side-channels from the Feitian A22 JavaCard, we use the Ledger Scaffold electronic board [17]. It provides several features really useful for side-channel attacks:

- native support of ISO7816, with possibility to easily spy all digital signals of the protocol thanks to SMA connectors (RESET, CLOCK and DATA);

- triggering capabilities easily configurable either on the APDU header processing, or on the APDU command processing;

- power measurement capabilities thanks to a clean PCB design, and a potentiometer allowing to manually adapt the gain of the measured power consumption thanks to a screw. Furthermore it is possible to activate 1kOhm resistors placed in serial on the ISO7816 digital signals, allowing to reduce the activity of the ISO7816 clock in the measured power consumption;

- the Ledger Scaffold is physically made of two parts: one *motherboard* (main part of Scaffold including the FPGA driving the board, all the electronic circuitry and the different connectors) and one *daughter board* (used to connect the target, and being interchangeable). Thus one can easily develop new *daughter boards*, for instance for having access to the different sides of the target. This is what NinjaLab has done with a custom smartcard daughter board that gives access to the opened side of the smartcard (see Figure 1.6).

The full setup is shown on Figure 1.6, to access the die we simply remove the white plastic of the smartcard above the die with a scalpel, we hence have access to its front side. The right subfigure shows the EM probe position over the die.

Figure 1.6: Feitian A22 JavaCard - EM Acquisition Setup

Figure 1.7 depicts a side-channel execution trace of an ECDSA signature acquired with the above setup. The acquisition is triggered thanks to the Scaffold board on the last byte of the ECDSA signature APDU command sent. On the figure, we identified the three major steps of ECDSA signature:

- 1. Initialization and generation of nonce k and random projective coordinate z

- 2. Scalar multiplication  $Q_{(x,y,z)} = [k]G_{(x,y,z)}$

- 3. Computation of the signature (r, s) from  $Q_{(x,y,z)}, h, d, k$

Figure 1.7: Feitian A22 JavaCard - EM Traces - ECDSA Signature

The Feitian A22 JavaCard and YubiKey 5Ci ECDSA signature EM activities look very similar, we will then work on Feitian A22 JavaCard and try to find a weakness in Infineon implementation. After fruitless attempts to find a vulnerability in the scalar multiplication, we focused our effort on the end of the computation and more precisely the nonce modular inversion because of a surprisingly *not* constant-time operation.

### 1.5.4 Focus on the Nonce Modular Inversion

Figure 1.8 is a zoom into the end of the ECDSA signature EM activity. The computation of (r, s) from  $[k]G_{(x,y,z)}, k, h, d$  amounts to:

- $r = z^{-1}x \mod p$

- $s = k^{-1}(h + rd) \mod N$

It seems pretty obvious to us that the two similar shaped operations (identified on Figure 1.8) correspond to the two modular inversions (which are the most complicated operations in the computation of (r, s)). Moreover, when observing several ECDSA signature executions, these operations seem to have different execution times.

Figure 1.8: Feitian A22 JavaCard – EM Traces – ECDSA Signature – (r, s) Computation

This observation is the beginning of a journey that will take two years to complete and a lot of efforts and disappointments but finally a success. This document tries to report this journey in its many details.

## Chapter 2

# Reverse-Engineering of the Modular Inversion

As mentioned in Chapter 1, we decided to analyze the nonce modular inversion of the Infineon ECDSA implementation due to the presence of a timing leakage. A timing leakage does not necessary mean that there is a vulnerability but it is surprising for such a sensitive operation. Indeed, revealing even a small number of bits of the nonce for several ECDSA signatures is enough for a complete key-recovery attack thanks to lattice reduction techniques (initially proposed in [10] and applied in many practical attacks since).

### 2.1 ECDSA Signature Traces

First, 1000 EM side-channel traces of ECDSA signature are acquired with the Feitian A22 JavaCard setup. For completeness, the acquisition details are given in Table 2.1. 1000 EM side-channel traces of the full ECDSA signature execution are acquired in about 7 hours.

### 2.1.1 Acquisition Campaign

| operation             | ECDSA signature                                        |

|-----------------------|--------------------------------------------------------|

| equipment             | PicoScope 6424E, Langer ICR HH 500-06                  |

| inputs                | Messages are random, Key is constant (randomly chosen) |

| number of operations  | 1000                                                   |

| length                | 120ms                                                  |

| sampling rate         | 5GSa/s                                                 |

| samples per trace     | 600MSamples                                            |

| channel(s)            | EM activity                                            |

| channel(s) parameters | DC 50ohms, $[-120, 80]$ mV                             |

| file size             | 600GB                                                  |

| acquisition time      | about 7 hours                                          |

Table 2.1: Acquisition parameters on Feitian A22 JavaCard - ECDSA Signature

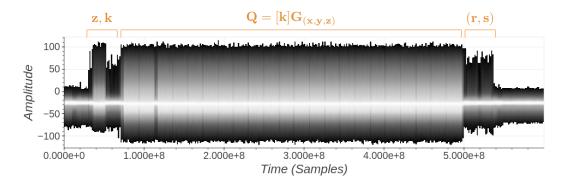

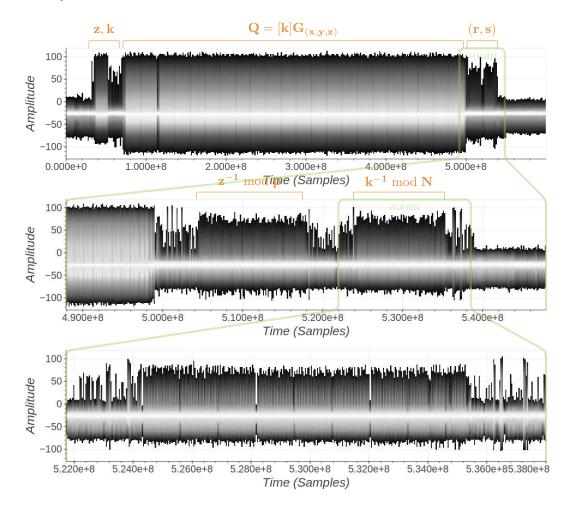

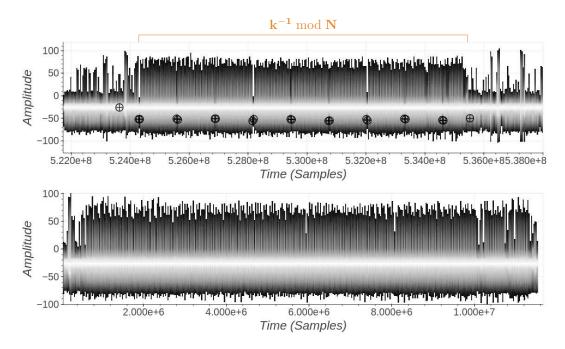

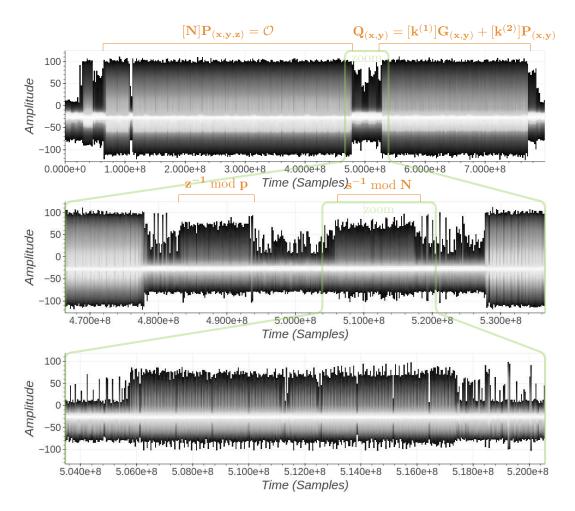

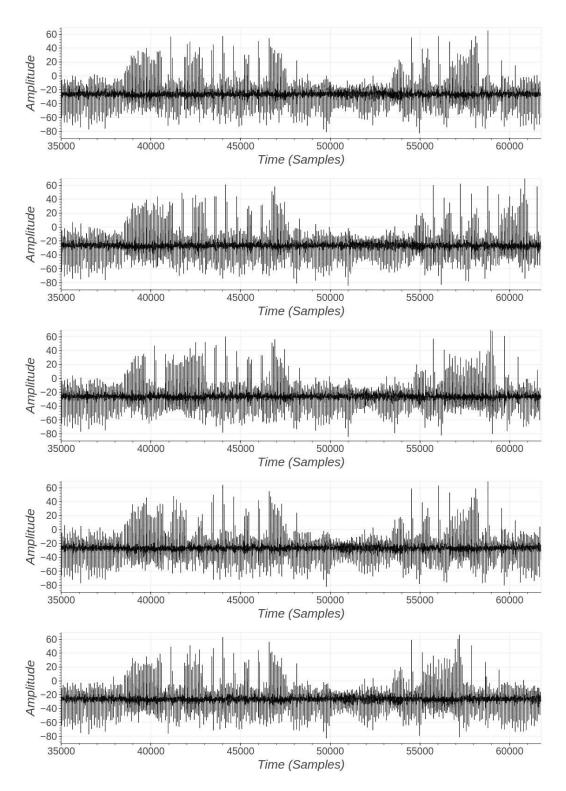

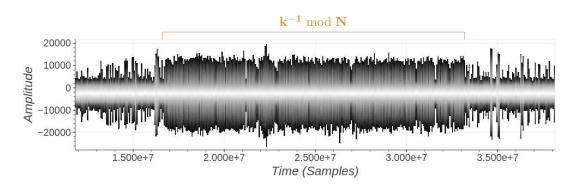

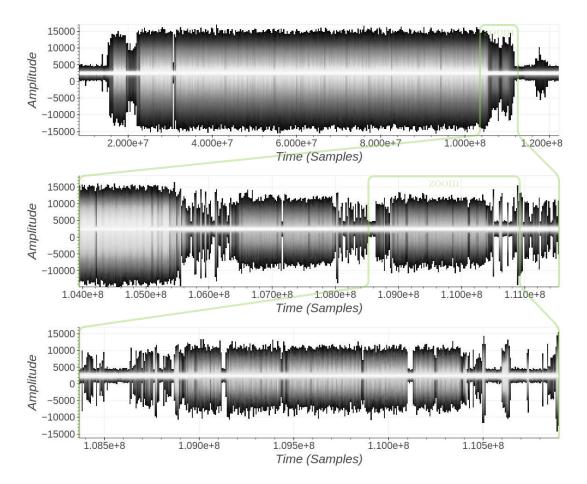

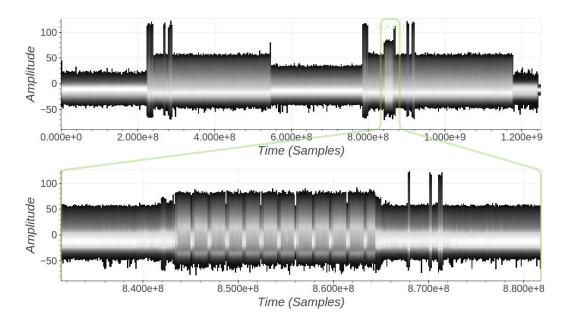

Figure 2.1 shows a single side-channel execution trace, where the modular inversion patterns are identified. We suppose that the second pattern corresponds to the nonce inversion and the first one (the closest to the scalar multiplication) relates to the inversion of the third projective coordinate of the resulting point Q. It just makes more sense but the operations could be done the other way around.

Figure 2.1: Feitian A22 JavaCard – ECDSA Signature – Full Trace (Top) - (r, s) Computation (Middle) -  $k^{-1} \mod N$  Computation (Bottom)

### 2.1.2 Side-Channel Analysis

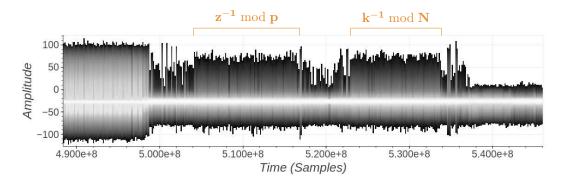

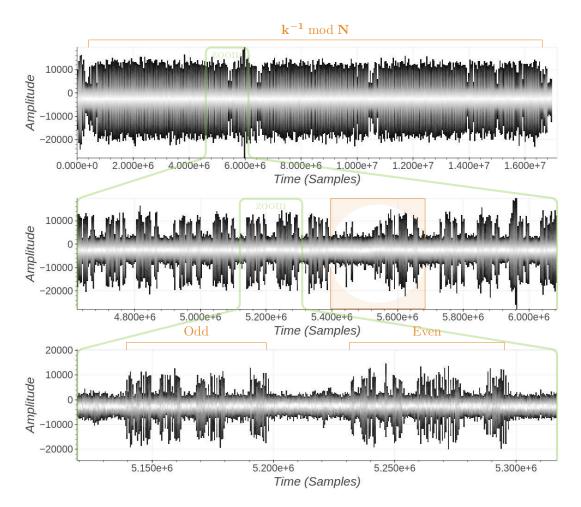

Now that we have many executions for various values of the nonce k (which is known here since the private key d is known, thanks to equation 1.1), let us look into the EM signal. Figure 2.2 bottom subfigure shows that the computation is an iterative process. Moreover, the process is regularly paused (as we can see on the figure). These pauses are quite easy to automatically detect (specially because they occur at a pretty stable period), the two black dots on the figure illustrate this automatic detection.

Figure 2.2: Feitian A22 JavaCard – ECDSA Signature –  $k^{-1} \mod N$  Computation (Top) – Zoom on Few Iterations (Bottom)

Figure 2.3 shows the result of this detection over the whole operation (top subfigure). Our first step is simply to remove these pauses as we suspect they are not related to the computation but to regular interrupts of the microcontroller. The second subfigure depicts a single subtrace (corresponding to the suspected modular inversion) after the removal of all pauses.

Figure 2.3: Feitian A22 JavaCard – ECDSA Signature –  $k^{-1} \mod N$  Computation – Interruptions Detection (Top) - Cleaned Trace (Bottom)

The next step is to detect all the operation iterations, this is done over all the 1000 ECDSA executions. The result is illustrated on Figure 2.4 first subfigure where each iteration is detected through the research of two anchors: the blue and black dots (see the second subfigure). This detection process is simply based on the amplitude of the signal and approximate length of an iteration. We cannot tell if the detection works perfectly over the whole set of 1000 traces but random visual checks over some traces make us pretty confident that we are not too wrong. One can also remark that some iterations are longer than others (or are preceded by pauses), as we can see in the middle of the second subfigure.

Figure 2.4: Feitian A22 JavaCard – ECDSA Signature –  $k^{-1} \mod N$  Computation – Iterations Detection (Top) - Zoom on Few Iterations (Bottom)

Now we have a precise estimate of the number of iterations of a modular iteration, we can validate that this number changes from one ECDSA execution to the other. When considering a modular inversion that is not constant time, our first hypothesis is the Extended Euclidean Algorithm (EEA for short).

### 2.1.3 First Hypothesis: Extended Euclidean Algorithm

Algorithm 1 recalls the computation of a modular inversion with the textbook EEA (there are many versions of the EEA and notably the binary version, but here the number of iterations observed would better match the classical EEA). If our hypothesis is correct, then the number of iterations detected previously should match the Algorithm 1 while loop iteration number (for the right inputs (k, N), where k is the nonce and N is the order of the elliptic curve). However, while the iteration count of EEA(k, N) (based on Algorithm 1) is always close to the number of detected iterations in the side-channel traces, it does not match exactly.

Algorithm 1: Extended Euclidean Algorithm for Modular Inversion

**Input** : v, n: two positive integers with  $v \le n$  and gcd(v, n) = 1**Output:**  $v^{-1} \mod n$ : the inverse of  $v \mod n$ 1  $r_0, r_1 \leftarrow n, v$ **2**  $t_0, t_1 \leftarrow 0, 1$ 3 while  $r_1 \neq 0$  do  $q \leftarrow \operatorname{div}(r_0, r_1)$  $\mathbf{4}$  $r_0, r_1 \leftarrow r_1, r_0 - q.r_1$  $\mathbf{5}$ 6  $t_0, t_1 \leftarrow t_1, t_0 - q.t_1$ 7 end s if  $t_0 < 0$  then 9  $t_0 \leftarrow t_0 + n$ 10 end 11 return  $t_0$

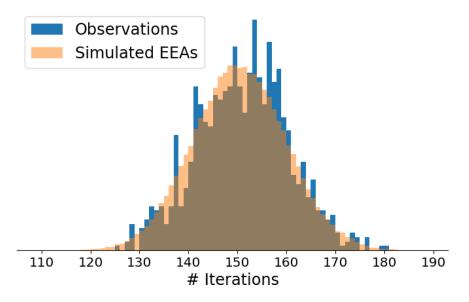

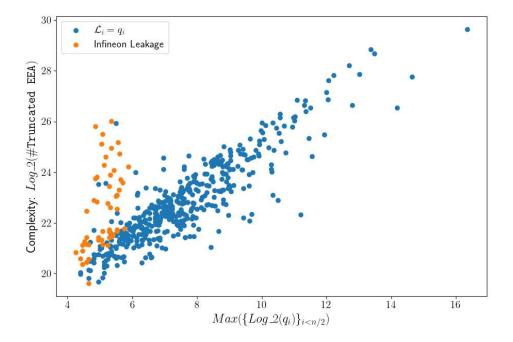

When plotting the distribution of the number of iterations over the 1000 observed operations with regard to the distribution of the number of iterations of random calls to EEA(x, N) with x a random value of same size as k, one can tell that the distribution matches. This is illustrated on Figure 2.5, confirming that we are observing the execution of an EEA, but not with the value of k.

Figure 2.5: Feitian A22 JavaCard – ECDSA Signature –  $k^{-1} \mod N$  Computation – Distribution of the Number of Iterations – Observations (Blue) - EEA Simulations (Orange)

After checking that the first modular inversion pattern was not the correct one (the inversion of z and k could have been done in the unnatural way), the next hypothesis is the presence of a side-channel countermeasure:

Hypothesis: k is *blinded* before its inversion.

This would make an attack much harder (and maybe impossible if the mask is large enough). Validating this hypothesis seems quite far-reaching, we rather first validate once for all that the identified operation is really a modular inversion using **EEA** before going deeper in this direction. One way to do so is to study the ECDSA signature verification execution.

## 2.2 ECDSA Signature Verification Traces

The ECDSA signature verification scheme involves the modular inversion of a public value (see the  $s^{-1} \mod N$  operation in the introductory chapter, Section 1.4.2). Let us bet that the developer did not protect this operation since it does not involve any secret.

### 2.2.1 Acquisition Campaign

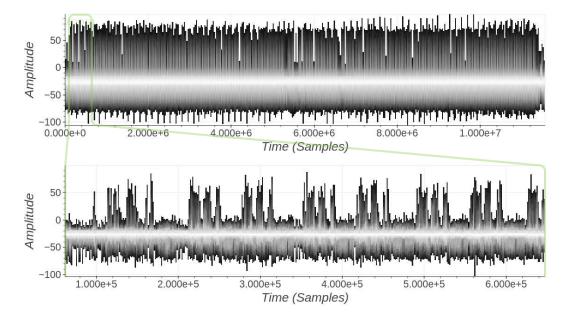

The acquisition campaign for the ECDSA signature verification operation is quite similar to that of the ECDSA signature operation, full details are given in Table 2.2. A single side-channel execution trace is displayed in Figure 2.6.

| operation             | ECDSA signature verification                                 |

|-----------------------|--------------------------------------------------------------|

| equipment             | PicoScope 6424E, Langer ICR HH 500-06                        |

| inputs                | Messages are random, Signature generated from a constant Key |

| number of operations  | 1000                                                         |

| length                | 160ms                                                        |

| sampling rate         | 5GSa/s                                                       |

| samples per trace     | 800MSamples                                                  |

| channel(s)            | EM activity                                                  |

| channel(s) parameters | DC 500hms, $[-120, 80]$ mV                                   |

| file size             | 800GB                                                        |

| acquisition time      | about 7 hours                                                |

|                       |                                                              |

Table 2.2: Acquisition parameters on Feitian A22 JavaCard – ECDSA Signature Verification

Figure 2.6: Feitian A22 JavaCard - ECDSA Signature Verification - Full Trace

### 2.2.2 Side-Channel Analysis

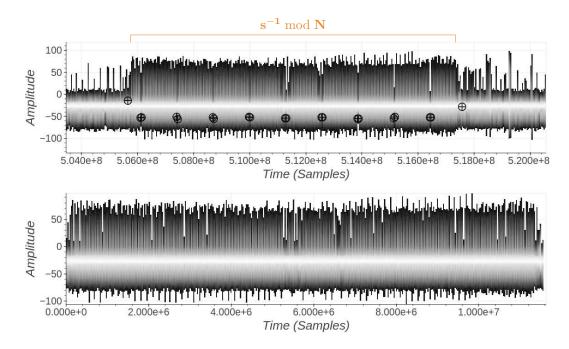

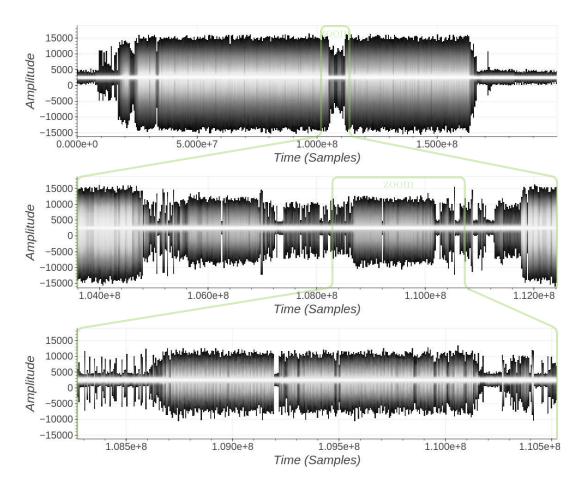

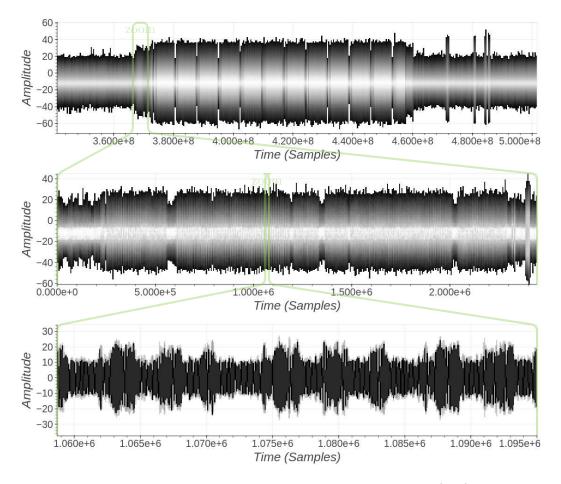

The analysis of the side-channel traces tells us the following (as illustrated in Figure 2.7):

- the first long operation is a secure scalar multiplication (very similar to the one observed in the ECDSA signature traces), we do not know its purpose. Maybe to check that the point P is on the curve (even though this seems a bit overkill);

- knowing the values  $k^{(1)}$  and  $k^{(2)}$  and observing the sequence of doubling and addition operations, it was easy to confirm that the last operation is a double scalar multiplication based on an unbalanced (*i.e.* naive) double-and-add algorithm;

- between the two scalar multiplication operations lies two modular inversion patterns similar to those of the signature algorithm. The first one is certainly owned by the previous scalar multiplication while the second one should be the computation of  $s^{-1} \mod N$ .

Figure 2.7: Feitian A22 JavaCard – ECDSA Signature Verification – Full Trace (Top) - Zoom Between the Scalar Multiplications (Middle) -  $s^{-1} \mod N$  Computation (Bottom)

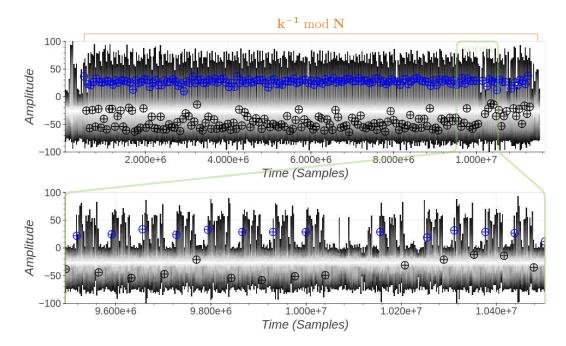

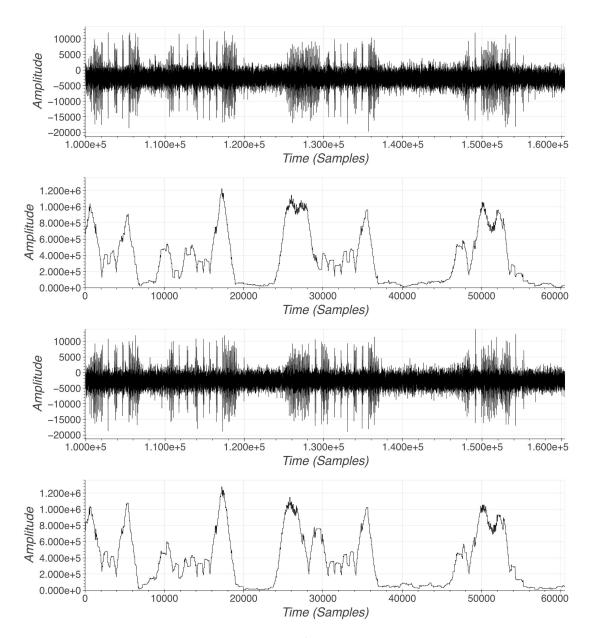

After the cleaning process of removing the interrupts (see Figure 2.8) and detecting each iteration (as illustrated in Figure 2.9) we could validate that the number of iterations perfectly matches the EEA number of iterations. This confirms without any doubt that the observed process is the EEA and let the hypothesis of a blinding countermeasure in the signature algorithm open.

Figure 2.8: Feitian A22 JavaCard – ECDSA Signature Verification –  $s^{-1} \mod N$  Computation – Interruptions Detection (Top) - Cleaned Trace (Bottom)

Figure 2.9: Feitian A22 JavaCard – ECDSA Signature Verification –  $s^{-1} \mod N$  Computation – Iterations Detection (Top) - Zoom on Few Iterations (Bottom)

Before coming back to the signature algorithm, we could relate the *large* iterations occurrence (as identified by the orange boxes on Figure 2.9, second subfigure) to the inner values of the EEA computation: the iteration is large if (and only if) the binary length difference between  $r_0$  and  $r_1$  (as computed in Algorithm 1, line 4) is larger than 5. In all the following we will denote the binary length difference between  $r_0$  and  $r_1$  as:

$$\Delta_{r_0,r_1} = len(r_0) - len(r_1).$$

### 2.2.3 A Timing Leakage

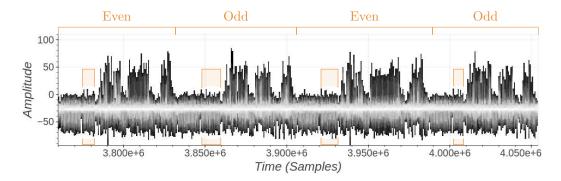

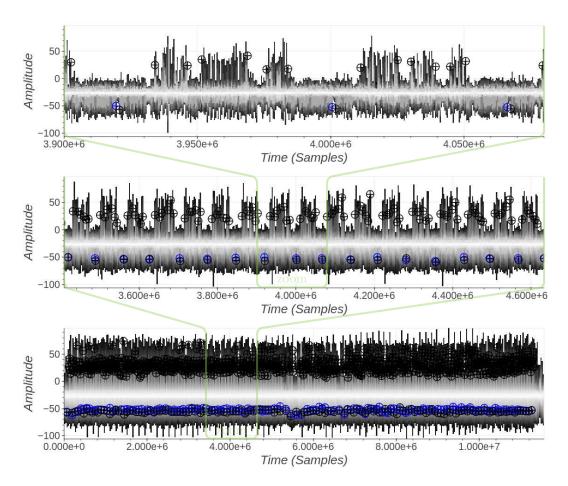

We have seen that the computation length of the inner iterations of the EEA is related to the value  $\Delta_{r_0,r_1}$  taken at the beginning of the iteration: the iteration is larger when  $\Delta_{r_0,r_1} > 5$ . In fact, the timing leakage is stronger than that. Figure 2.10 shows four consecutive iterations (none of them are *large*, *i.e.*  $\Delta_{r_0,r_1} \leq 5$ ), two observations can be made:

- *Odd* versus *Even* iterations are different, we will have to treat them differently (and have no explanation for this observation);

- a small part at the beginning of each iteration is varying in length (identified with orange boxes).

Figure 2.10: Feitian A22 JavaCard – ECDSA Signature Verification –  $s^{-1} \bmod N$  – Four Consecutive Iterations

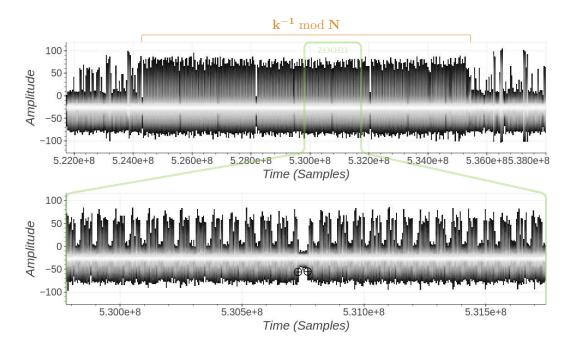

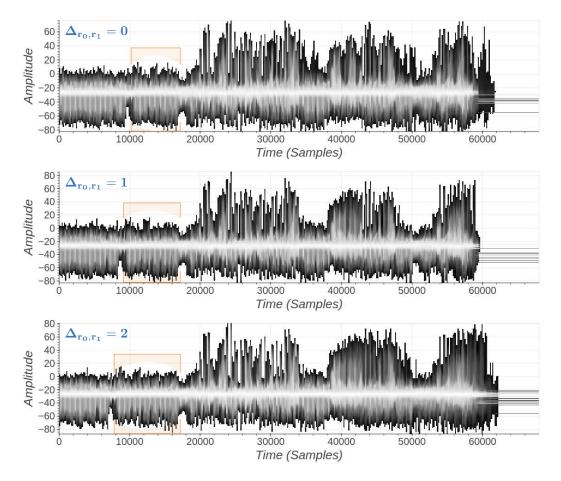

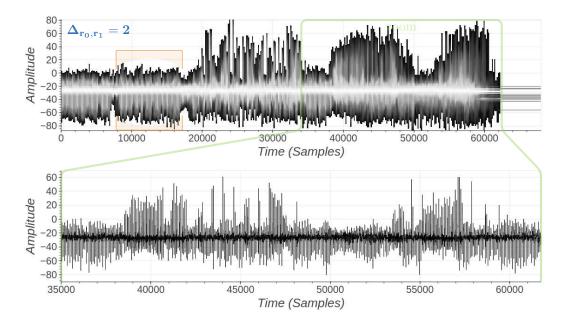

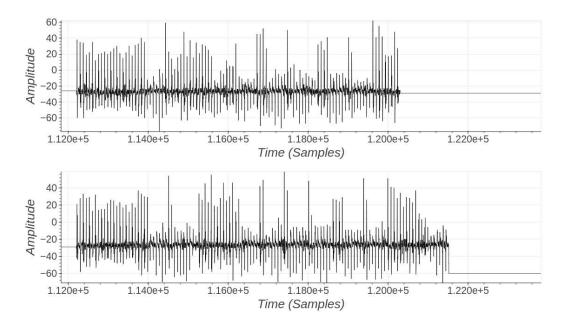

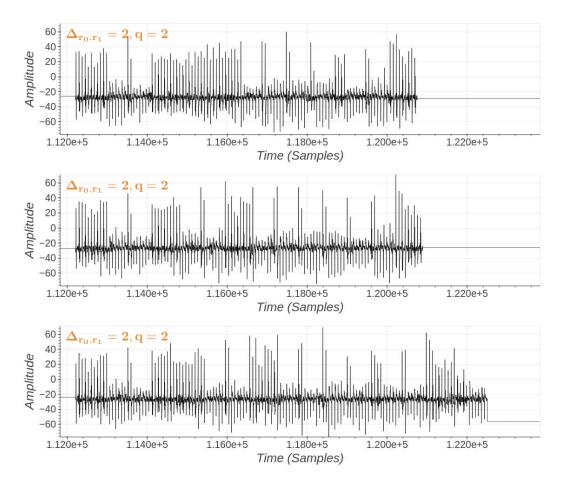

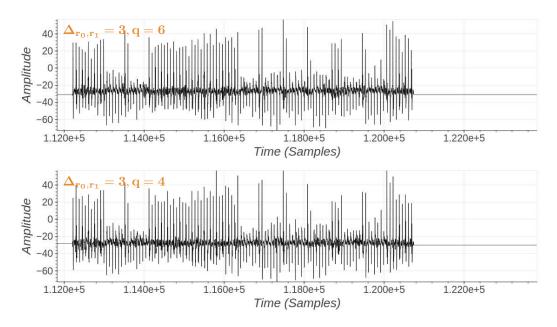

Thanks to the  $\Delta_{r_0,r_1} > 5$  timing leakage that stands out clearly, we easily found out that the execution time is directly proportional to the value  $\Delta_{r_0,r_1}$  as displayed on Figure 2.11 where iterations are synchronized and regrouped with constant values of  $\Delta_{r_0,r_1}$ .

Figure 2.11: Feitian A22 JavaCard – ECDSA Signature Verification – 100 Superposed Odd Iterations –  $\Delta_{r_0,r_1} = 0$  (Top) -  $\Delta_{r_0,r_1} = 1$  (Middle) -  $\Delta_{r_0,r_1} = 2$  (Bottom)

## 2.3 Reverse-Engineering of the Modular Inversion Countermeasure

Let us now get back to the blinding countermeasure hypothesis and try to confirm and better understand it.

### 2.3.1 Hypothesis

A simple and cost-effective way to protect the modular inversion of the nonce in ECDSA is to use a multiplicative mask. Hence, instead of computing directly the inverse of k, one can compute the inverse of k' defined as:

$k' = m \times k \bmod N,$

where m is a non-null positive integer. Once inverted,  $k^{-1} \mod N$  can be easily computed from  $k'^{-1} \mod N$  by another modular multiplication by m.

This countermeasure seems really interesting because it only costs 2 modular multiplications (a quite cheap operation when the secure microcontroller embeds a modular arithmetic co-processor) to protect a modular inversion (a much more expensive operation). Also, if we consider that m is generated with a similar entropy than k itself, retrieving k' by side-channel analysis would provide zero information about the nonce value k and then the attack would be meaningless. However, the real cost of the countermeasure lies in the generation of m and if the random number generator is expensive, it might be tempting to reduce the size of m.

Now, let us suppose that Infineon developers decided to reduce the length of m to something small enough to be brute-forced, then by retrieving k' by side-channel analysis one could brute force the value of k and then recover the ECDSA long term private key. So let us hope for the best (adversary-wise) and try to validate this.

#### 2.3.2 Brute-force Experiments

We build an experiment that would validate that the multiplicative mask is small:

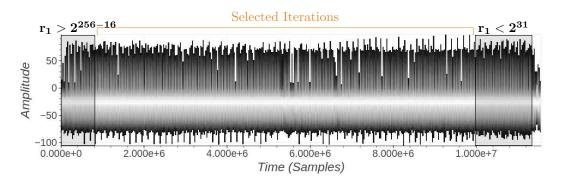

Since the private key is known on the Feitian A22 JavaCard setup, we can compute, for each ECDSA execution, the nonce value k (as per equation 1.1). We are looking for the value of the mask m such that  $k' = m \times k \mod N$ . To discriminate the possible values of m we have the information extracted from the side-channel execution traces of EEA(k', N). In a preliminary test, we decided to test all non-zero values of m of binary length 32 or less. We then select a mask candidate m if EEA $(m \times k \mod N, N)$  has the exact same number of iterations than the side-channel execution trace of EEA(k', N) and if the number and positions of the large iterations (i.e. iterations for which  $\Delta_{r_0,r_1} > 5$ ) also match. We apply this process to the first 10 traces of the signature acquisition campaign. At the end of this 32-bit brute-force, we end-up with:

- 3 mask candidates for the first trace;

- 38035 mask candidates for the  $10^{th}$  trace;

- a unique mask candidate for the other 8 traces.

The  $10^{th}$  trace only shows a single large iteration ( $\Delta_{r_0,r_1} > 5$ ), the first trace has 4 such iterations, all other traces have 4 or more large iterations. Since our mask detection is mainly based on the position of these large iterations, it makes quite sense that the more an **EEA** execution shows large iterations, the fewer mask candidates are left. The fact that, for all 10 traces, there exists at least one mask candidate left is very promising and comforts ourselves in the assumption that Infineon uses a multiplicative mask countermeasure with a 32-bit mask.

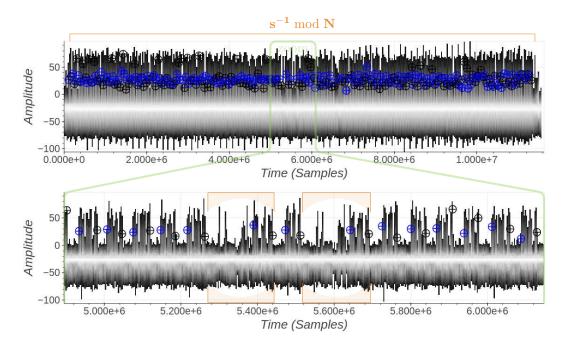

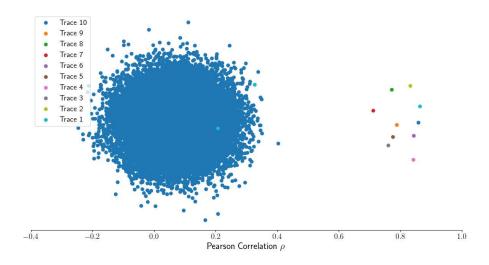

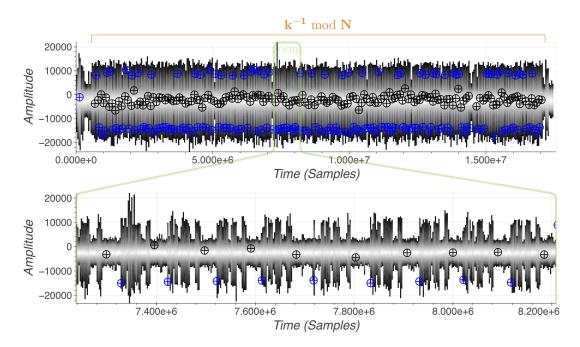

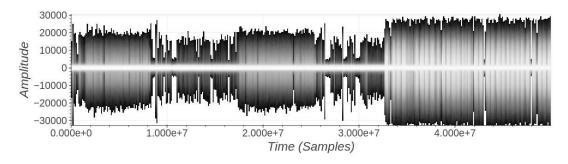

Now we have seen in the previous section that a finer-grain timing leakage appears for each iteration. We can use this leakage to try and discriminate one mask candidate among several. To do so, we automatically identify the timing leakage start and end positions (as illustrated in Figure 2.11) for each iteration of the first 10 ECDSA side-channel execution traces. This detection, without being perfect, works well enoug for our test. We then have, for all iterations, the length (in time samples) of the timing leakage area. We previously observed that this area length is proportional to the value  $\Delta_{r_0,r_1}$ . A good way to capture this linear relation is to use the Pearson correlation [8], we then compute the Pearson correlation  $\rho$  between the sequence of  $\Delta_{r_0,r_1}$  values computed from the execution simulation of EEA( $m \times k \mod N, N$ ) for a mask candidate m and the observed sequence of time sample lengths extracted from the side-channel

execution trace of EEA(k', N) (and denoted  $\{\mathcal{L}_i\}_{0 < i < n}$  for an *n* iterations EEA).

Figure 2.12 displays the Pearson correlation results for each candidate of each trace <sup>1</sup> (each trace has a different color, *e.g.* the blue dots represent the 10th trace with all its 38K mask candidates). It appears clearly that, for each trace, a single mask candidate stands out clearly with a high correlation ( $\rho > 0.7$ ) while all other candidates stay well below  $\rho < 0.5$ .

Figure 2.12: Feitian A22 JavaCard – Modular Inversion Multiplicative Mask Brute Force – Pearson Correlation Results  $\rho(\{\Delta_{r_0,r_1i}\}_{0 < i \le n}, \{\mathcal{L}_i\}_{0 < i \le n})$

This experiment, without being a formal proof, finishes to convince us that we have understood the masking countermeasure of Infineon to protect the modular inversion of the nonce.

## 2.4 Conclusions

Algorithm 1 is validated, the nonce is blinded with a multiplicative mask of size 32 bits (and odd). Moreover, we identified a timing leakage proportional with  $\Delta_{r_0,r_1} = len(r_0) - len(r_1)$  ( $r_0$  and  $r_1$  appearing in line 4 of Algorithm 1). In the next chapter, we will consider a side-channel attacker able to soundly (*i.e.* without error) extract the value  $\Delta_{r_0,r_1}$  for each and every iteration of an **EEA** execution.

<sup>&</sup>lt;sup>1</sup>We randomly spread the correlation results over the y-axis following a Gaussian distribution of mean 0 and standard deviation  $10^{-2}$  for illustration purpose.

## Chapter 3

# Input-Recovery Attack on the Extended Euclidean Algorithm

Let us recall the EEA algorithm here:

| <b>Algorithm 1:</b> Extended Euclidean Algorithm for Modular Inversion (repeated from page 26) |

|------------------------------------------------------------------------------------------------|

|                                                                                                |

| <b>Input</b> : $v, n$ : two positive integers with $v \le n$ and $gcd(v, n) = 1$               |

| <b>Output:</b> $v^{-1} \mod n$ : the inverse of $v \mod n$                                     |

| $r_0, r_1 \leftarrow n, v$                                                                     |

| 2 $t_0, t_1 \leftarrow 0, 1$                                                                   |

| 3 while $r_1 \neq 0$ do                                                                        |